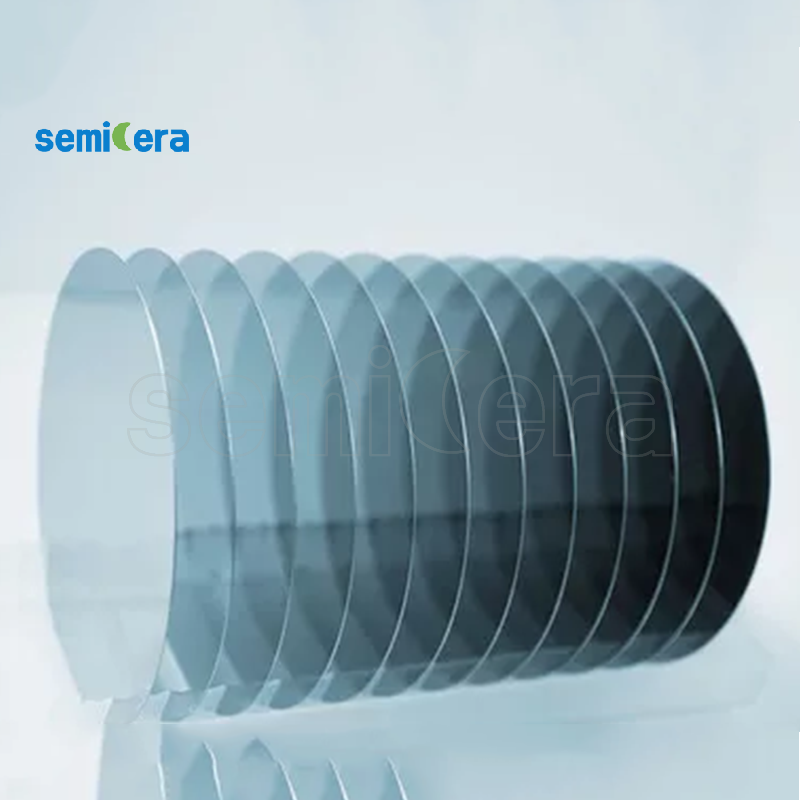

Semicerastellt de850V High Power GaN-op-Si Epi Wafer, en Duerchbroch an der Halbleiterinnovatioun. Dës fortgeschratt Epi Wafer kombinéiert déi héich Effizienz vu Gallium Nitride (GaN) mat der Käschteneffizienz vum Silicon (Si), fir eng mächteg Léisung fir Héichspannungsapplikatiounen ze kreéieren.

Schlëssel Features:

•Héich Volt Ëmgank: Entworf fir bis zu 850V z'ënnerstëtzen, ass dëse GaN-on-Si Epi Wafer ideal fir erfuerderlech Kraaftelektronik, wat méi Effizienz a Leeschtung erméiglecht.

•Erweidert Power Dicht: Mat superior Elektronenmobilitéit an thermescher Konduktivitéit erlaabt d'GaN Technologie kompakt Designen a verstäerkter Kraaftdicht.

•Käschten-effikass Léisung: Andeems Dir Silizium als Substrat benotzt, bitt dësen Epi Wafer eng kosteneffektiv Alternativ zu traditionelle GaN Wafers, ouni Kompromëss op Qualitéit oder Leeschtung.

•Breet Applikatioun Gamme: Perfekt fir ze benotzen an Power Converter, RF Verstärker, an aner High-Power elektronesch Geräter, fir Zouverlässegkeet an Haltbarkeet ze garantéieren.

Entdeckt d'Zukunft vun der Héichspannungstechnologie mat Semicera's850V High Power GaN-op-Si Epi Wafer. Designt fir opzedeelen Uwendungen, dëst Produkt garantéiert datt Är elektronesch Geräter mat maximaler Effizienz an Zouverlässegkeet funktionnéieren. Wielt Semicera fir Är nächst Generatioun Hallefleitbedierfnesser.

| Artikelen | Produktioun | Fuerschung | Dummy |

| Crystal Parameteren | |||

| Polytyp | 4H | ||

| Uewerfläch Orientéierung Feeler | <11-20 >4±0,15° | ||

| Elektresch Parameteren | |||

| Dopant | n-Typ Stickstoff | ||

| Resistivitéit | 0,015-0,025 Ohm·cm | ||

| Mechanesch Parameteren | |||

| Duerchmiesser | 150,0 ± 0,2 mm | ||

| Dicke | 350 ± 25 μm | ||

| Primär flaach Orientéierung | [1-100]±5° | ||

| Primär flaach Längt | 47,5 ± 1,5 mm | ||

| Secondaire Appartement | Keen | ||

| TTV | ≤5 μm | ≤10 μm | ≤15 μm |

| LTV | ≤3 μm (5mm*5mm) | ≤5 μm (5mm*5mm) | ≤10 μm (5mm*5mm) |

| Boun | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Warp | ≤35 μm | ≤45 μm | ≤55 μm |

| Front (Si-Face) Rauhegkeet (AFM) | Ra≤0.2nm (5μm*5μm) | ||

| Struktur | |||

| Mikropipe Dicht | <1 e/cm2 | <10 e/cm2 | <15 e/cm2 |

| Metal Gëftstoffer | ≤5E10 Atom/cm2 | NA | |

| BPD | ≤1500 ea/cm2 | ≤3000 ea/cm2 | NA |

| TSD | ≤500 ea/cm2 | ≤1000 ea/cm2 | NA |

| Front Qualitéit | |||

| Front | Si | ||

| Surface Finish | Si-Gesiicht CMP | ||

| Partikel | ≤60ea/wafer (Gréisst≥0.3μm) | NA | |

| Kratzer | ≤5 ea/mm. Kumulativ Längt ≤ Duerchmiesser | Kumulativ Längt≤2*Duerchmiesser | NA |

| Orangeschielen / Pits / Flecken / Sträifen / Rëss / Kontaminatioun | Keen | NA | |

| Kantchips / Abriecher / Fraktur / Hexplacke | Keen | ||

| Polytype Beräicher | Keen | Kumulative Beräich ≤20% | Kumulativ Beräich ≤30% |

| Front Laser Marquage | Keen | ||

| Zréck Qualitéit | |||

| Back Finish | C-Gesiicht CMP | ||

| Kratzer | ≤5ea/mm, Kumulativ Längt≤2*Duerchmiesser | NA | |

| Réckdefekter (Randchips/Abrécken) | Keen | ||

| Réck roughness | Ra≤0.2nm (5μm*5μm) | ||

| Réck Laser Marquage | 1 mm (vun uewen Rand) | ||

| Rand | |||

| Rand | Chamfer | ||

| Verpakung | |||

| Verpakung | Epi-prett mat Vakuumverpackung Multi-Wafer Kassett Verpakung | ||

| * Notizen: "NA" heescht keng Ufro Artikelen déi net ernimmt kënne bezéie sech op SEMI-STD. | |||