Iwwersiicht vun Semiconductor Prozess

De Halbleiterprozess involvéiert haaptsächlech d'Uwendung vu Mikrofabrizéierung a Filmtechnologien fir Chips an aner Elementer a verschiddene Regiounen, wéi Substrate a Rummen, voll ze verbannen. Dëst erliichtert d'Extraktioun vu Leadklemmen an d'Verkapselung mat engem Plastikisolatiounsmedium fir en integréierte Ganzt ze bilden, presentéiert als dreidimensional Struktur, a schlussendlech de Hallefleitverpackungsprozess ofgeschloss. D'Konzept vum Halbleiterprozess bezitt sech och op déi schmuel Definitioun vun der Halbleiter Chipverpackung. Aus enger méi breeder Perspektiv bezitt et sech op Verpackungstechnik, wat d'Verbindung an d'Befestigung vum Substrat involvéiert, d'Konfiguratioun vun der entspriechender elektronescher Ausrüstung, an e komplette System mat staarker ëmfaassender Leeschtung ze bauen.

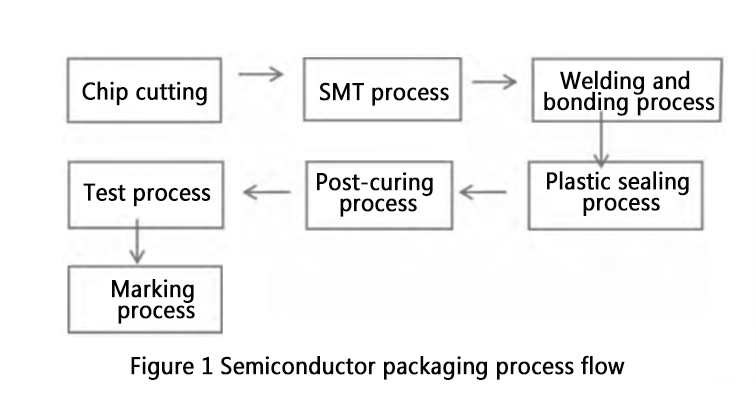

Semiconductor Verpakung Prozess Flow

De Semiconductor Verpackungsprozess enthält verschidde Aufgaben, wéi illustréiert an der Figur 1. All Prozess huet spezifesch Ufuerderungen an enk verbonne Workflows, déi eng detailléiert Analyse während der praktescher Etapp erfuerderen. De spezifesche Inhalt ass wéi follegt:

1. Chip Ausschneiden

Am Halbleiterverpackungsprozess, Chipschneiden involvéiert Siliziumwaferen an eenzel Chips ze schneiden an d'Siliziumschutt prompt ewechzehuelen fir Hindernisser fir spéider Aarbecht a Qualitéitskontroll ze vermeiden.

2. Chip Opriichte

Den Chipmontageprozess konzentréiert sech op d'Vermeidung vum Circuitschued beim Waferschleifen andeems Dir eng Schutzfilmschicht applizéiert, konsequent d'Integritéit vum Circuit betount.

3. Drot Bonding Prozess

D'Kontroll vun der Qualitéit vum Drotverbindungsprozess beinhalt d'Benotzung vun verschiddenen Zorte vu Golddrot fir d'Bindingspads vum Chip mat de Frame Pads ze verbannen, fir sécherzestellen datt den Chip mat externe Circuiten verbënnt an d'Gesamtprozessintegritéit behalen. Typesch ginn dotéiert Golddrot a Legierung Golddrot benotzt.

Dotéiert Golddrot: Typen enthalen GS, GW, an TS, gëeegent fir High-Arc (GS:>250 μm), mëttel-héich Arc (GW: 200-300 μm), a mëttel-niddereg Arc (TS: 100-200) μm) Bindung respektiv.

Alloyed Gold Wires: Typen enthalen AG2 an AG3, gëeegent fir Low-Arc Bonding (70-100 μm).

D'Duerchmiesser Optiounen fir dës Drot Gamme vun 0,013 mm ze 0,070 mm. Wiel vun de passenden Typ an Duerchmiesser baséiert op operationell Ufuerderunge an Normen ass entscheedend fir Qualitéitskontroll.

4. Molding Prozess

D'Haaptschaltung a Formelementer beinhalt d'Verkapselung. D'Kontroll vun der Qualitéit vum Schimmelprozess schützt d'Komponenten, besonnesch vu externe Kräfte, déi ënnerschiddlech Grad vu Schued verursaachen. Dëst beinhalt eng grëndlech Analyse vun de physikaleschen Eegeschafte vun de Komponenten.

Dräi Haaptmethoden ginn am Moment benotzt: Keramikverpackung, Plastiksverpackung an traditionell Verpakung. D'Gestioun vum Undeel vun all Verpackungsart ass entscheedend fir weltwäit Chipproduktiounsufuerderunge gerecht ze ginn. Wärend dem Prozess sinn iwwergräifend Fäegkeeten erfuerderlech, sou wéi d'Virheizung vum Chip a Leadrahmen virun der Verkapselung mat Epoxyharz, Schimmel a Post-Schimmelhärten.

5. Post-Curing Prozess

Nom Schimmelprozess ass d'Post-Aushärtbehandlung erfuerderlech, konzentréiert sech op d'Ewechhuele vun iwwerschësseg Materialien ronderëm de Prozess oder Package. Qualitéitskontroll ass wesentlech fir d'Gesamtprozessqualitéit an d'Erscheinung ze vermeiden.

6.Test Prozess

Wann déi vireg Prozesser ofgeschloss sinn, muss d'Gesamtqualitéit vum Prozess mat fortgeschrattem Testtechnologien an Ariichtungen getest ginn. Dëse Schrëtt beinhalt eng detailléiert Opnam vun Daten, konzentréiert sech op ob den Chip normalerweis op Basis vu sengem Leeschtungsniveau funktionnéiert. Wéinst den héije Käschte vun Testausrüstung ass et entscheedend Qualitéitskontroll uechter d'Produktiounsstadien z'erhalen, inklusiv visuell Inspektioun an elektresch Leeschtungstester.

Elektresch Performance Testen: Dëst beinhalt d'Test vun integréierte Circuiten mat automateschen Testausrüstung a garantéiert datt all Circuit richteg fir elektresch Tester ugeschloss ass.

Visuell Inspektioun: Techniker benotzen Mikroskope fir déi fäerdeg verpackte Chips grëndlech z'inspektéieren fir sécherzestellen datt se fräi vu Mängel sinn an d'Qualitéitsnormen vun der Halbleiterverpackung entspriechen.

7. Marquage Prozess

De Markéierungsprozess beinhalt d'Iwwerdroung vun de geteste Chips an en hallef fäerdeg Lagerhaus fir d'Finale Veraarbechtung, Qualitéitsinspektioun, Verpakung a Versand. Dëse Prozess enthält dräi Haaptschrëtt:

1) Electroplating: No der Form vun de Leads gëtt en Anti-Korrosiounsmaterial applizéiert fir Oxidatioun a Korrosioun ze vermeiden. Elektroplating Oflagerungstechnologie gëtt typesch benotzt well déi meescht Leads aus Zinn sinn.

2) Béie: Déi veraarbechte Leads ginn dann geformt, mam integréierte Circuitstreifen an engem Leadformungsinstrument gesat, kontrolléiert d'Leadform (J oder L Typ) an d'Uewerflächemontéiert Verpackung.

3) Laser Dréckerei: Endlech ginn déi geformte Produkter mat engem Design gedréckt, deen als speziell Mark fir den Halbleiterverpackungsprozess déngt, wéi an der Figur 3 illustréiert.

Erausfuerderungen a Recommandatiounen

D'Studie vun de Hallefleitverpackungsprozesser fänkt mat engem Iwwerbléck vun der Hallefleittechnologie un fir seng Prinzipien ze verstoen. Als nächst ass d'Untersuchung vum Verpackungsprozessflow zielt fir virsiichteg Kontroll während Operatiounen ze garantéieren, raffinéiert Gestioun benotzt fir Routineprobleemer ze vermeiden. Am Kontext vun der moderner Entwécklung ass d'Identifikatioun vun Erausfuerderunge bei Hallefleitverpackungsprozesser wesentlech. Et ass recommandéiert op Qualitéitskontroll Aspekter ze konzentréieren, grëndlech Meeschtesch Schlëssel Punkten ze effektiv de Prozess Qualitéit verbesseren.

Analyséiert aus enger Qualitéitskontroll Perspektiv, ginn et bedeitend Erausfuerderunge wärend der Ëmsetzung wéinst ville Prozesser mat spezifeschen Inhalter an Ufuerderungen, déi all déi aner beaflossen. Richteg Kontroll ass néideg während praktesch Operatiounen. Andeems Dir eng virsiichteg Aarbechtshaltung unhëlt an fortgeschratt Technologien applizéiert, kënnen d'Halbleiterverpackungsprozessqualitéit an d'technesch Niveaue verbessert ginn, fir eng ëmfaassend Applikatiounseffizienz ze garantéieren an exzellent allgemeng Virdeeler z'erreechen.(wéi an der Figur 3 gewisen).

Post Zäit: Mee-22-2024