1.About Integréiert Circuiten

1.1 D'Konzept an d'Gebuert vun integréierte Circuiten

Integréiert Circuit (IC): bezitt sech op en Apparat deen aktiv Geräter wéi Transistoren an Dioden kombinéiert mat passive Komponenten wéi Widderstänn a Kondensatoren duerch eng Serie vu spezifesche Veraarbechtungstechniken.

E Circuit oder System deen op engem Hallefleit (wéi Silizium oder Verbindungen wéi Galliumarsenid) "integréiert" ass wafer no bestëmmte Circuitverbindungen an dann an enger Schuel verpackt fir spezifesch Funktiounen auszeféieren.

1958 huet den Jack Kilby, dee fir d'Miniaturiséierung vun elektronescher Ausrüstung bei Texas Instruments (TI) verantwortlech war, d'Iddi vun integréierte Circuits proposéiert:

"Well all Komponente wéi Kondensatoren, Widderstänn, Transistoren, asw. aus engem Material gemaach kënne ginn, hunn ech geduecht datt et méiglech wier se op e Stéck Halbleitermaterial ze maachen an se dann mateneen ze verbannen fir e komplette Circuit ze bilden."

Den 12. an den 19. September 1958 huet de Kilby d'Fabrikatioun an d'Demonstratioun vum Phase-Shift Oszillator an Ausléiser ofgeschloss, respektiv, wat d'Gebuert vum integréierte Circuit markéiert.

Am Joer 2000 gouf de Kilby mam Nobelpräis an der Physik ausgezeechent. Den Nobelpräiskomitee huet eemol kommentéiert datt Kilby "de Grondlag fir modern Informatiounstechnologie geluecht huet."

D'Bild hei drënner weist Kilby a säin integréierte Circuit Patent:

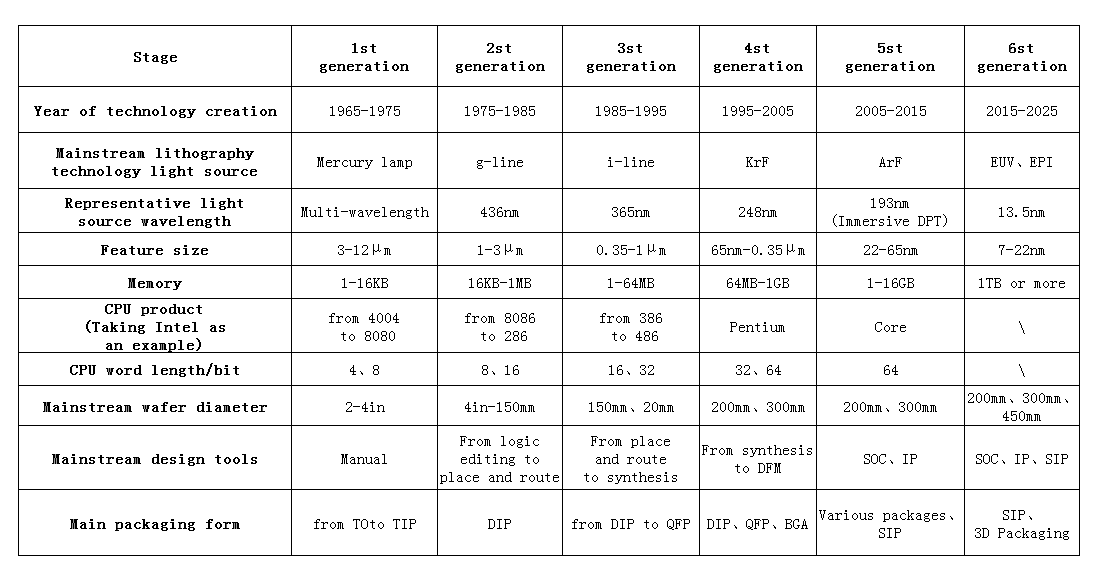

1.2 Entwécklung vun semiconductor Fabrikatioun Technologie

Déi folgend Figur weist d'Entwécklungsstadien vun der Semiconductor Fabrikatioun Technologie:

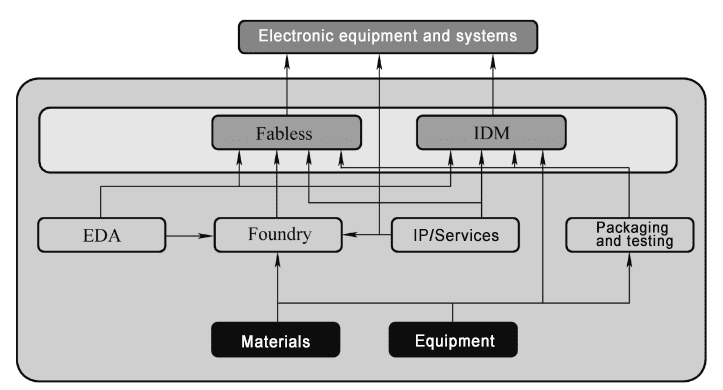

1.3 Integréiert Circuit Industrie Kette

D'Zesummesetzung vun der Halbleiterindustrie Kette (haaptsächlech integréiert Kreesleef, dorënner diskret Apparater) ass an der Figur uewen gewisen:

- Fabless: Eng Firma déi Produkter ouni Produktiounslinn designt.

- IDM: Integréiert Geräthersteller, integréiert Geräthersteller;

- IP: Kreesmodulhersteller;

- EDA: Elektronesch Design Automatesch, elektronesch Designautomatiséierung, d'Firma bitt haaptsächlech Design Tools;

- Schmelz; Wafer Schmelz, bitt Chip Fabrikatioun Servicer;

- Verpakung an Testen Schmelz Firmen: haaptsächlech Fabless an IDM Déngscht;

- Material a speziell Ausrüstungsfirmen: bitt haaptsächlech déi néideg Materialien an Ausrüstung fir Chipfabrikatiounsfirmen.

D'Haaptprodukter produzéiert mat Hallefleittechnologie sinn integréiert Kreesleef an diskret Hallefleitgeräter.

D'Haaptprodukter vun integréierte Circuiten enthalen:

- Applikatioun spezifesch Standard Parts (ASSP);

- Mikroprozessor Eenheet (MPU);

- Erënnerung

- Applikatioun Spezifesch Integréiert Circuit (ASIC);

- Analog Circuit;

- Allgemeng Logik Circuit (Logical Circuit).

D'Haaptrei Produkter vun semiconductor diskret Apparater enthalen:

- Diode;

- Transistor;

- Power Apparat;

- Héich-Volt Apparat;

- Mikrowellengerät;

- Optoelektronik;

- Sensor Apparat (Sensor).

2. Integréiert Circuit Fabrikatioun Prozess

2.1 Chip Fabrikatioun

Dosende oder souguer Zéngdausende vu spezifesche Chips kënne gläichzäiteg op engem Siliziumwafer gemaach ginn. D'Zuel vun de Chips op engem Siliziumwafer hänkt vun der Aart vum Produkt an der Gréisst vun all Chip of.

Silicon wafers ginn normalerweis Substrate genannt. Den Duerchmiesser vu Siliziumwaferen ass iwwer d'Jore eropgaang, vu manner wéi 1 Zoll am Ufank bis op déi allgemeng benotzt 12 Zoll (ongeféier 300 mm) elo, a mécht en Iwwergang op 14 Zoll oder 15 Zoll.

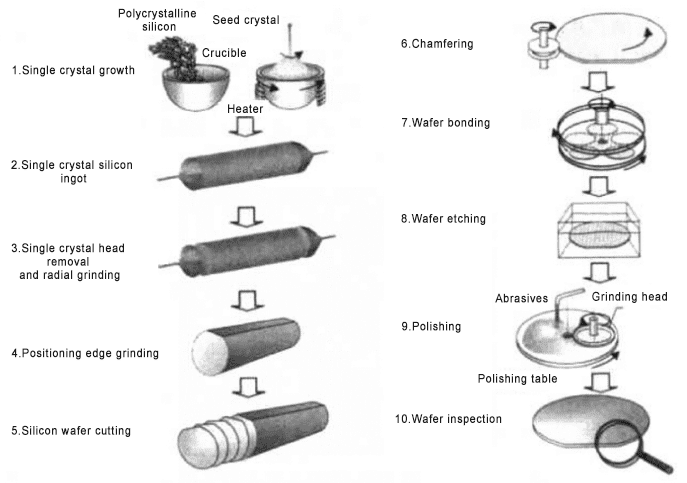

Chip Fabrikatioun ass allgemeng a fënnef Etappen opgedeelt: Silicon wafer Virbereedung, Silicon wafer Fabrikatioun, Chip Testen / Picking, Assemblée a Verpakung, an Finale Testen.

(1)

Silicon wafer Virbereedung:

Fir de Rohmaterial ze maachen, gëtt Silizium aus Sand extrahéiert a gereinegt. E spezielle Prozess produzéiert Silizium Ingots mat passenden Duerchmiesser. D'Ingots ginn dann an dënn Siliziumwafere geschnidden fir Mikrochips ze maachen.

Wafere ginn op spezifesch Spezifikatioune virbereet, sou wéi Ufuerderunge fir Registréierungsrand a Kontaminatiounsniveauen.

(2)Silicon wafer Fabrikatioun:

Och bekannt als Chipfabrikatioun, kënnt de bloe Siliziumwafer an d'Siliziumwafer Fabrikatiounsanlag a geet dann duerch verschidde Botzen, Filmbildung, Photolithographie, Ätzen an Doping Schrëtt. De veraarbechte Siliziumwafer huet e komplette Set vun integréierte Circuits permanent op der Siliziumwafer geätzt.

(3)Testen a Selektioun vu Siliziumwafers:

Nodeems d'Siliconwafer Fabrikatioun ofgeschloss ass, ginn d'Siliconwafers an d'Test / Sortéierungsgebitt geschéckt, wou eenzel Chips gepréift an elektresch getest ginn. Akzeptabel an inakzeptabel Chips ginn dann zortéiert, a defekt Chips ginn markéiert.

(4)Assemblée a Verpakung:

Nom Wafer Testen / Sortéieren, ginn d'Wafers an d'Versammlung an d'Verpakungsschrëtt an d'individuell Chips an e Schutzröhre Package. Déi hënnescht Säit vum Wafer gëtt gemoolt fir d'Dicke vum Substrat ze reduzéieren.

En décke Plastikfilm ass op der Réck vun all Wafer befestegt, an dann gëtt eng Diamant-Spëtzt Sägeblatt benotzt fir d'Chips op all Wafer laanscht d'Schrëftlinnen op der viischter Säit ze trennen.

De Plastikfilm op der Récksäit vun der Siliciumwafer hält de Siliziumchip aus ze falen. An der Versammlungsanlag ginn déi gutt Chips gedréckt oder evakuéiert fir e Montagepaket ze bilden. Spéider gëtt den Chip an enger Plastiks- oder Keramik-Schuel versiegelt.

(5)Finale Test:

Fir d'Funktionalitéit vum Chip ze garantéieren, gëtt all verpakten integréierte Circuit getest fir den elektreschen an Ëmweltcharakteristesche Parameter Ufuerderunge vum Hiersteller ze treffen. Nom finalen Test gëtt den Chip un de Client geschéckt fir op enger spezieller Plaz ze montéieren.

2.2 Prozess Divisioun

Integréiert Circuit Fabrikatiounsprozesser ginn allgemeng opgedeelt an:

Front-Enn: De Front-End-Prozess bezitt sech allgemeng op d'Fabrikatiounsprozess vun Apparater wéi Transistoren, haaptsächlech d'Formatiounsprozesser vun Isolatioun, Gatestruktur, Quell an Drain, Kontakt Lächer, etc.

Back-Enn: De Back-End Prozess bezitt sech haaptsächlech op d'Bildung vu Verbindungslinnen, déi elektresch Signaler op verschidden Apparater op den Chip iwwerdroe kënnen, haaptsächlech Prozesser wéi dielektresch Oflagerung tëscht Verbindungslinnen, Metalllinnbildung a Leadpad-Formatioun.

Mëtt-Etapp: Fir d'Performance vun Transistoren ze verbesseren, fortgeschratt Technologie Noden no 45nm / 28nm benotzen High-k Gate Dielectrics a Metal Gate Prozesser, a addéiere Ersatz Gate Prozesser a lokal Interconnect Prozesser nodeems d'Transistor Quell an Drain Struktur virbereet ass. Dës Prozesser sinn tëscht dem Front-End-Prozess an dem Back-End-Prozess, a ginn net an traditionelle Prozesser benotzt, sou datt se Mid-Stage Prozesser genannt ginn.

Normalerweis ass de Kontakt Lach Virbereedungsprozess d'Trennlinn tëscht dem Front-End Prozess an dem Back-End Prozess.

Kontakt Lach: e Lach, dat vertikal an der Siliziumwafer geprägt ass, fir d'éischt Schicht Metallverbindungslinn an de Substratapparat ze verbannen. Et ass mat Metall wéi Wolfram gefüllt a gëtt benotzt fir d'Apparatelektrode an d'Metallverbindungsschicht ze féieren.

Duerch Hole: Et ass de Verbindungswee tëscht zwou ugrenzend Schichten vu Metallverbindungslinnen, déi an der dielektrescher Schicht tëscht den zwou Metallschichten läit, an ass allgemeng mat Metaller wéi Kupfer gefëllt.

An engem breede Sënn:

Front-End Prozess: Am breede Sënn soll integréiert Circuit Fabrikatioun och Testen, Verpakung an aner Schrëtt enthalen. Verglach mat Testen a Verpakung, Komponente an interconnect Fabrikatioun sinn den éischten Deel vun integréiert Circuit Fabrikatioun, kollektiv als Front-Enn Prozesser bezeechent;

Back-End Prozess: Testen a Verpakung ginn Back-End Prozesser genannt.

3. Anhang

SMIF: Standard mechanesch Interface

AMHS: Automatiséiert Material Handing System

OHT: Overhead Hoist Transfer

FOUP: Front Ouverture Unified Pod, Exklusiv op 12 Zoll (300 mm) Wafers

Méi wichteg,Semicera kënne biddengraphite Deeler, mëll/steif Filz,Siliziumkarbid Deeler, CVD Siliziumkarbid Deeler,an anSiC / TaC Beschichtete Deelermat vollem Halbleiterprozess an 30 Deeg.Mir freeën eis oprecht Äre laangfristeg Partner a China ze ginn.

Post Zäit: Aug-15-2024