Semicerastellt seng héich Qualitéit virSi EpitaxieServicer, entworf fir déi exakt Norme vun der haiteger Hallefleitindustrie ze treffen. Epitaxial Siliziumschichten si kritesch fir d'Performance an d'Zouverlässegkeet vun elektroneschen Apparater, an eis Si Epitaxy-Léisungen garantéieren datt Är Komponenten optimal Funktionalitéit erreechen.

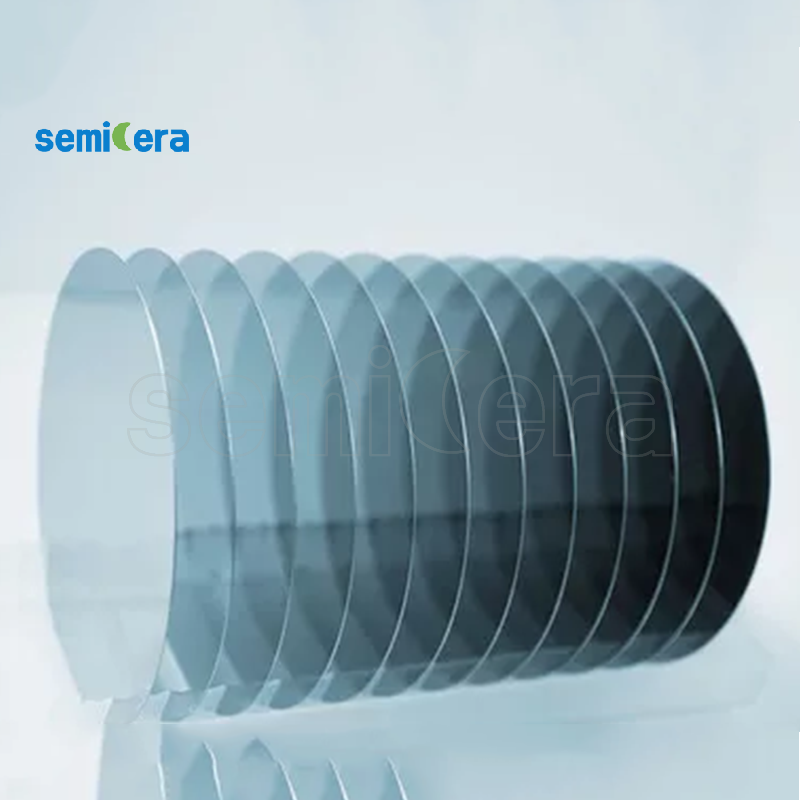

Präzisioun gewuess Silicon Schichten Semiceraversteet datt d'Fundament vun High-Performance-Geräter an der Qualitéit vun de benotzte Materialien läit. EisSi EpitaxieProzess gëtt virsiichteg kontrolléiert fir Siliziumschichten mat aussergewéinlecher Uniformitéit a Kristallintegritéit ze produzéieren. Dës Schichten si wesentlech fir Uwendungen rangéiert vu Mikroelektronik bis fortgeschratt Kraaftapparater, wou Konsistenz an Zouverlässegkeet wichteg sinn.

Optimiséiert fir Gerät LeeschtungDéiSi EpitaxieServicer vun Semicera ugebuede ginn ugepasst fir d'elektresch Eegeschafte vun Ären Apparater ze verbesseren. Andeems Dir Siliziumschichten mat héijer Rengheet mat gerénger Defektdensitéit wuessen, suerge mir fir datt Är Komponenten op hir Bescht Leeschtunge, mat verbesserter Carrier Mobilitéit a miniméierter elektrescher Resistivitéit. Dës Optimiséierung ass kritesch fir d'Héichgeschwindegkeet an d'Effizienz Charakteristiken z'erreechen, déi vun der moderner Technologie gefuerdert sinn.

Villsäitegkeet an Uwendungen Semicera'sSi Epitaxieass gëeegent fir eng breet Palette vun Uwendungen, dorënner d'Produktioun vun CMOS Transistoren, Power MOSFETs, a bipolare Kräizung Transistoren. Eise flexiblen Prozess erlaabt d'Personaliséierung baséiert op de spezifesche Viraussetzunge vun Ärem Projet, egal ob Dir dënn Schichten fir Héichfrequenz Uwendungen oder méi décker Schichten fir Kraaftapparater braucht.

Superior Material QualitéitQualitéit ass am Häerz vun allem wat mir bei Semicera maachen. EisSi EpitaxieProzess benotzt Staat-vun-der-Konscht Ausrüstung an Techniken ze suergen, datt all Silicon Layer den héchste Standarden vun Rengheet an strukturell Integritéit meets. Dës Opmierksamkeet op Detailer miniméiert d'Optriede vu Mängel, déi d'Leeschtung vum Apparat beaflosse kënnen, wat zu méi zouverlässeg a méi laang dauerhafte Komponenten resultéiert.

Engagement fir Innovatioun Semiceraass engagéiert fir un der Spëtzt vun der Hallefleittechnologie ze bleiwen. EisSi EpitaxieServicer reflektéieren dëst Engagement, déi lescht Fortschrëtter an epitaxial Wuesstumstechniken integréiert. Mir verfeineren eis Prozesser kontinuéierlech fir Siliziumschichten ze liwweren déi den evoluéierende Bedierfnesser vun der Industrie entspriechen, fir datt Är Produkter kompetitiv um Maart bleiwen.

Mooss Léisunge fir Är BesoinenVerstoen datt all Projet eenzegaarteg ass,Semicerabitt personaliséiertSi EpitaxieLéisunge fir Äre spezifesche Besoinen ze passen. Egal ob Dir speziell Dopingprofiler, Schichtdecken oder Uewerflächefinishen braucht, eist Team schafft enk mat Iech zesummen fir e Produkt ze liwweren dat Äre präzise Spezifikatioune entsprécht.

| Artikelen | Produktioun | Fuerschung | Dummy |

| Crystal Parameteren | |||

| Polytyp | 4H | ||

| Uewerfläch Orientéierung Feeler | <11-20 >4±0,15° | ||

| Elektresch Parameteren | |||

| Dopant | n-Typ Stickstoff | ||

| Resistivitéit | 0,015-0,025 Ohm·cm | ||

| Mechanesch Parameteren | |||

| Duerchmiesser | 150,0 ± 0,2 mm | ||

| Dicke | 350 ± 25 μm | ||

| Primär flaach Orientéierung | [1-100]±5° | ||

| Primär flaach Längt | 47,5 ± 1,5 mm | ||

| Secondaire Appartement | Keen | ||

| TTV | ≤5 μm | ≤10 μm | ≤15 μm |

| LTV | ≤3 μm (5mm*5mm) | ≤5 μm (5mm*5mm) | ≤10 μm (5mm*5mm) |

| Boun | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Warp | ≤35 μm | ≤45 μm | ≤55 μm |

| Front (Si-Face) Rauhegkeet (AFM) | Ra≤0.2nm (5μm*5μm) | ||

| Struktur | |||

| Mikropipe Dicht | <1 e/cm2 | <10 e/cm2 | <15 e/cm2 |

| Metal Gëftstoffer | ≤5E10 Atom/cm2 | NA | |

| BPD | ≤1500 ea/cm2 | ≤3000 ea/cm2 | NA |

| TSD | ≤500 ea/cm2 | ≤1000 ea/cm2 | NA |

| Front Qualitéit | |||

| Front | Si | ||

| Surface Finish | Si-Gesiicht CMP | ||

| Partikel | ≤60ea/wafer (Gréisst≥0.3μm) | NA | |

| Kratzer | ≤5 ea/mm. Kumulativ Längt ≤ Duerchmiesser | Kumulativ Längt≤2*Duerchmiesser | NA |

| Orangeschielen / Pits / Flecken / Sträifen / Rëss / Kontaminatioun | Keen | NA | |

| Kantchips / Abriecher / Fraktur / Hexplacke | Keen | ||

| Polytype Beräicher | Keen | Kumulative Beräich ≤20% | Kumulativ Beräich ≤30% |

| Front Laser Marquage | Keen | ||

| Zréck Qualitéit | |||

| Back Finish | C-Gesiicht CMP | ||

| Kratzer | ≤5ea/mm, Kumulativ Längt≤2*Duerchmiesser | NA | |

| Réckdefekter (Randchips/Abrécken) | Keen | ||

| Réck roughness | Ra≤0.2nm (5μm*5μm) | ||

| Réck Laser Marquage | 1 mm (vun uewen Rand) | ||

| Rand | |||

| Rand | Chamfer | ||

| Verpakung | |||

| Verpakung | Epi-prett mat Vakuumverpackung Multi-Wafer Kassett Verpakung | ||

| * Notizen: "NA" heescht keng Ufro Artikelen déi net ernimmt kënne bezéie sech op SEMI-STD. | |||