Applikatioun Feld

1. Héich-Vitesse integréiert Circuit

2. Mikrowellengeräter

3. Héich Temperatur integréiert Circuit

4. Muecht Apparater

5. Niddereg Muecht integréiert Circuit

6. MEMS

7. Niddereg Volt integréiert Circuit

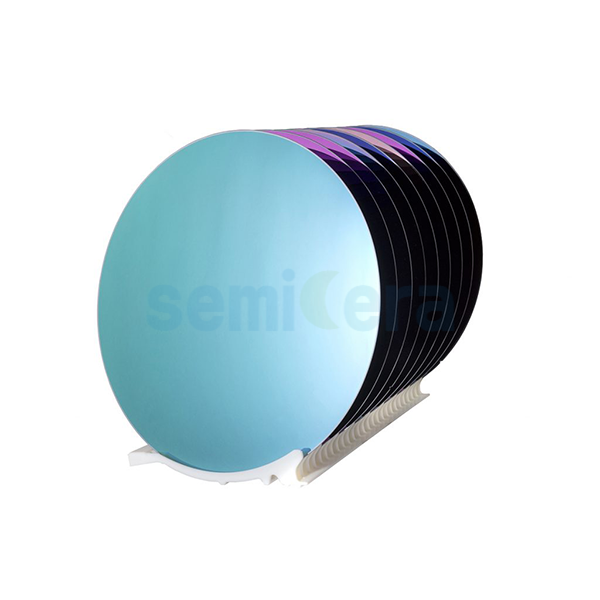

| Artikel | Argument | |

| Allgemeng | Wafer Duerchmiesser | 50/75/100/125/150/200 mm ± 25 um |

| Bogen/Warp | <10 um | |

| Partikel | 0,3 um<30 ea | |

| Flaach / Notch | Flaach oder Notch | |

| Rand Ausgrenzung | / | |

| Apparat Layer | Apparat-Layer Typ / Dopant | N-Typ / P-Typ |

| Apparat-Layer Orientatioun | <1-0-0> / <1-1-1> / <1-1-0> | |

| Apparat-Layer Dicke | 0,1-300 um | |

| Apparat-Layer Resistivitéit | 0.001 ~ 100.000 ohm-cm | |

| Apparat-Layer Partikel | <30ea@0.3 | |

| Apparat Layer TTV | <10 um | |

| Apparat Layer Finish | Poléiert | |

| BOX | Begruewe thermesch Oxid Dicke | 50nm(500Å)~15um |

| Handle Layer | Handle Wafer Typ / Dopant | N-Typ / P-Typ |

| Handle Wafer Orientatioun | <1-0-0> / <1-1-1> / <1-1-0> | |

| Handle Wafer Resistivitéit | 0.001 ~ 100.000 ohm-cm | |

| Handle Wafer Dicke | >100 um | |

| Handle Wafer Finish | Poléiert | |

| SOI wafers vun Zil Spezifikatioune kënnen no Client Ufuerderunge personaliséiert ginn. | ||